.

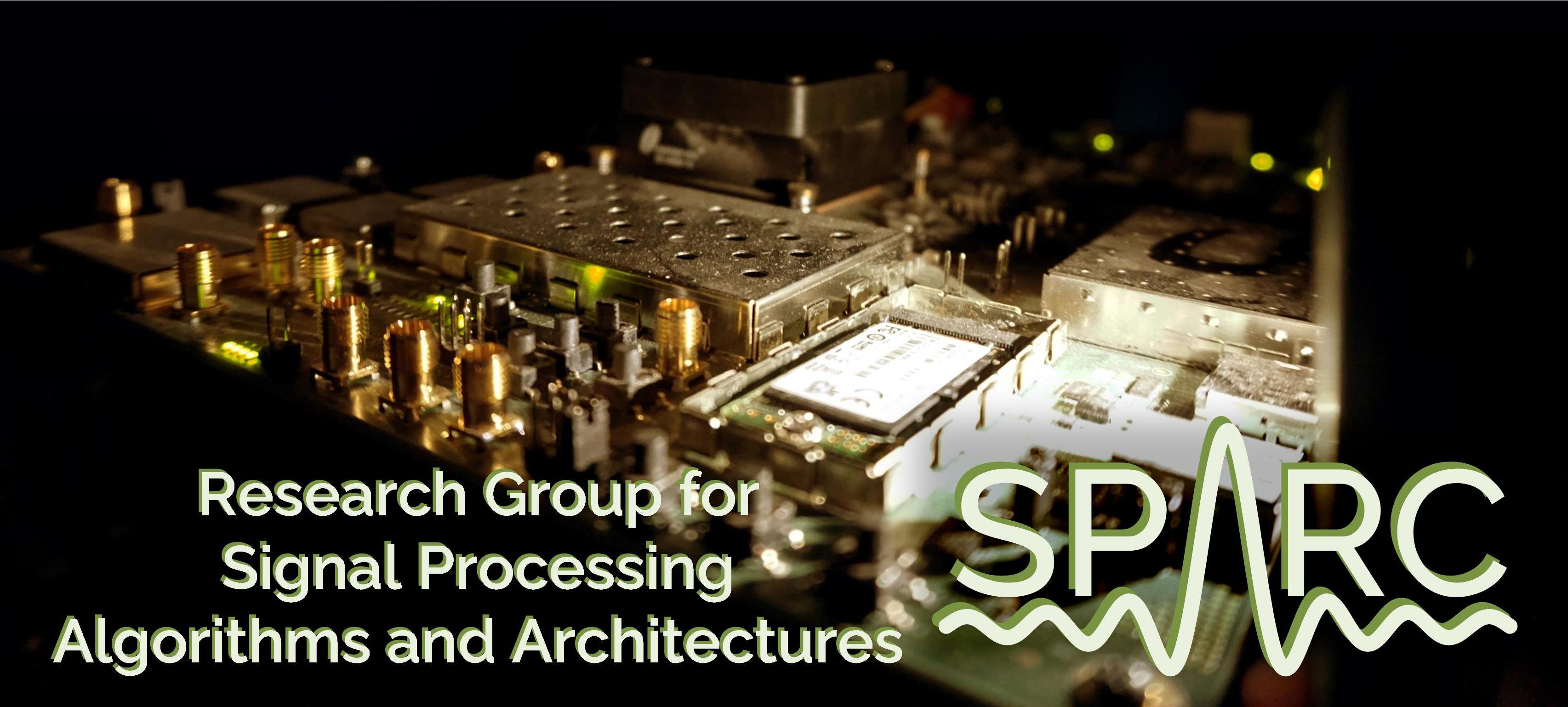

SPARC

Research group for Signal Processing Algorithms and Architectures (SPARC) is situated at the University of Belgrade - School of Electrical Engineering (ETF), at the Department of electronics. Our research focuses on the design of signal processing algorithms and efficient hardware architectures. We develop energy, resource-utilization, and cost efficient solutions applicable in digital signal processing, digital image processing, channel coding, communication systems, machine learning, and biomedical systems.

We welcome you to our website and invite you to explore our projects and research!

.

NEWS

Dec. 31, 2021

Oct. 14, 2021

PEOPLE

Lazar Saranovac

Professor

Born in Sremska Mitrovica, Serbia, in 1961. Received the B.S. degree in electrical engineering and the M.S. and Ph.D. degrees in electronics from the University of Belgrade, Serbia, in 1987, 1993, and 2001, respectively. His research interests include embedded systems, digital signal processing, and design of digital systems.

Dragomir El Mezeni

Assistant Professor

Born in Belgrade, Serbia, in 1985. Received the B.S. degree in electrical engineering and the M.S. and Ph.D. degrees in electronics from the University of Belgrade, Serbia, in 2008, 2010, and 2018, respectively. His research interests include digital image/video processing, computational photography, and very large scale integration architectures for digital signal processing.

Vladimir Petrović

Assistant Professor

Received the Dipl.-Ing., M.S., and Ph.D. degrees in electrical engineering from the University of Belgrade, Serbia, in 2014, 2015, and 2021, respectively. His research interests include VLSI design, communication systems architectures, digital signal processing, and hardware implementations of signal processing algorithms.

Nemanja Filipović

Ph.D. Student

Received the Dipl. Ing. and M.S. degrees in electrical engineering from the University of Belgrade, Serbia, in 2019 and 2020, respectively. He is currently a Ph.D. student at the same university. In 2018 he joined Tannera LLC, where he works as a hardware engineer. His research interests include VLSI design, communication systems architectures, digital signal processing, and hardware implementations of signal processing algorithms.

Živana Garašević

Ph.D. Student, Research Assistant

Received the Dipl. Ing. and M.S. degrees in electrical engineering from the University of Belgrade, Serbia, in 2020 and 2022, respectively. She enrolled the Ph.D. studies at the same university in 2022. Her research interests include LDPC coding, VLSI design, and hardware implementations of signal processing algorithms.

Nikola Borović

Ph.D. Student, Research Assistant

Received the Dipl. Ing. and M.Sc. degrees in electrical engineering from the University of Belgrade, Serbia, in 2022 and 2023, respectively. He is currently a Ph.D. student at the same university. His research interests include polar coding, VLSI design, and hardware implementations of signal processing algorithms.

Danilo Đokić

Ph.D. Student, Teaching & Research Assistant

Received the Dipl. Ing. and M.Sc. degrees in electrical and computer engineering, in 2016 and 2021, respectively, from the School of Electrical Engineering, University of Belgrade, Serbia where he is currently working toward the Ph.D. degree. He is also Teaching Assistant at the same department. His research interests include signal processing, RF and FPGA design.

PROJECTS

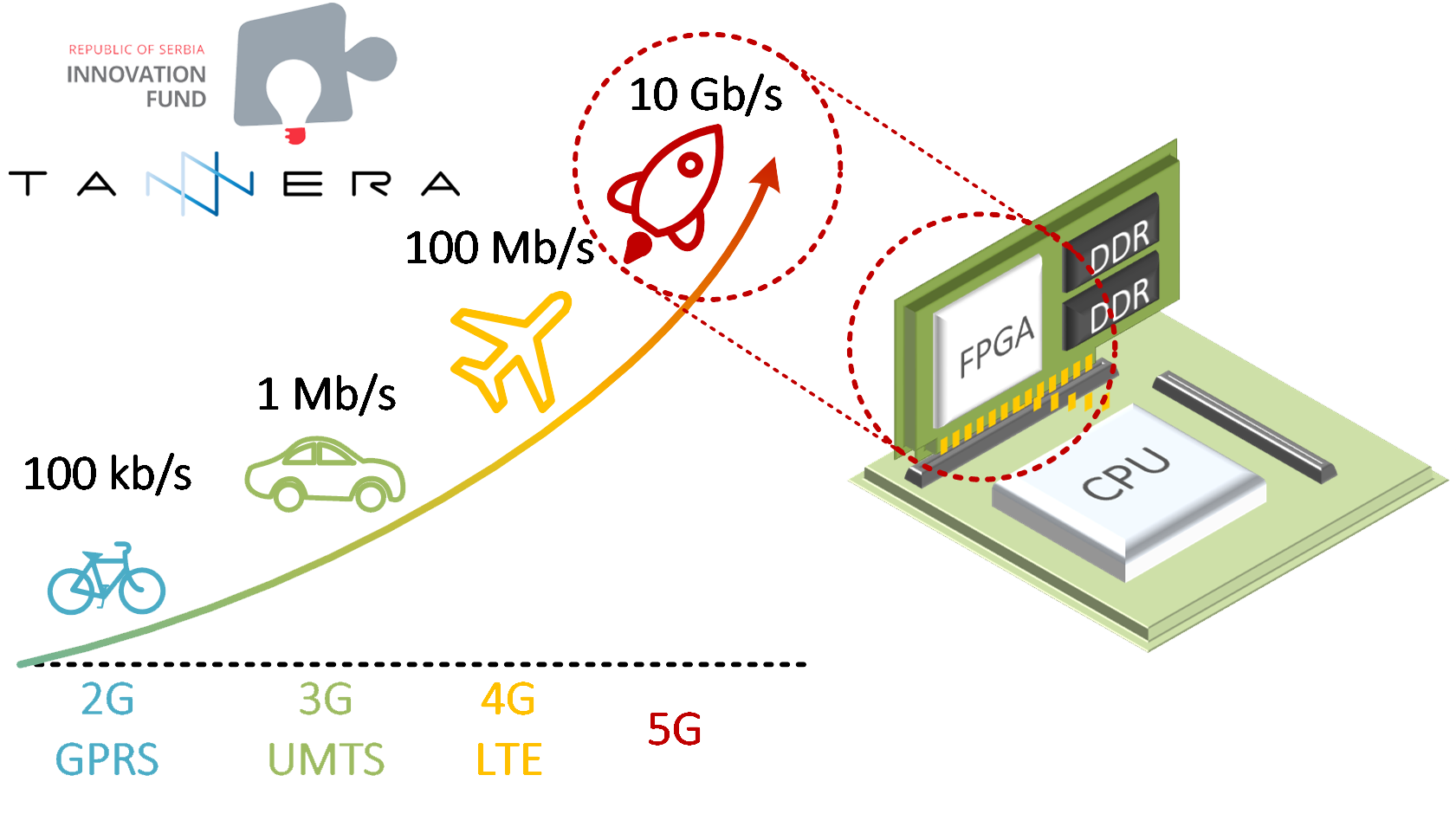

Accelerate 5G

Funded by: Innovation Fund, Tannera

Start date: Mar. 2022

Project leads: dr. Vladimir Petrović and dr. Dragomir El Mezeni, SPARC group

LEAD TEAMAccelerate 5G: Hardware accelerator IP cores for 5G infrastructure is a project whose objective is to develop a full cost-efficient product of an end-to-end FPGA based accelerator for physical layer processing in 5G base stations. The focus is on workloads placed at the distributing units, which include compute intensive tasks, such as forward error correction, modulation, and channel equalization. The product will be in the form of IP cores that can be deployed to any FPGA acceleration card. Acceleration will significantly reduce the total cost of ownership for 5G infrastructure.

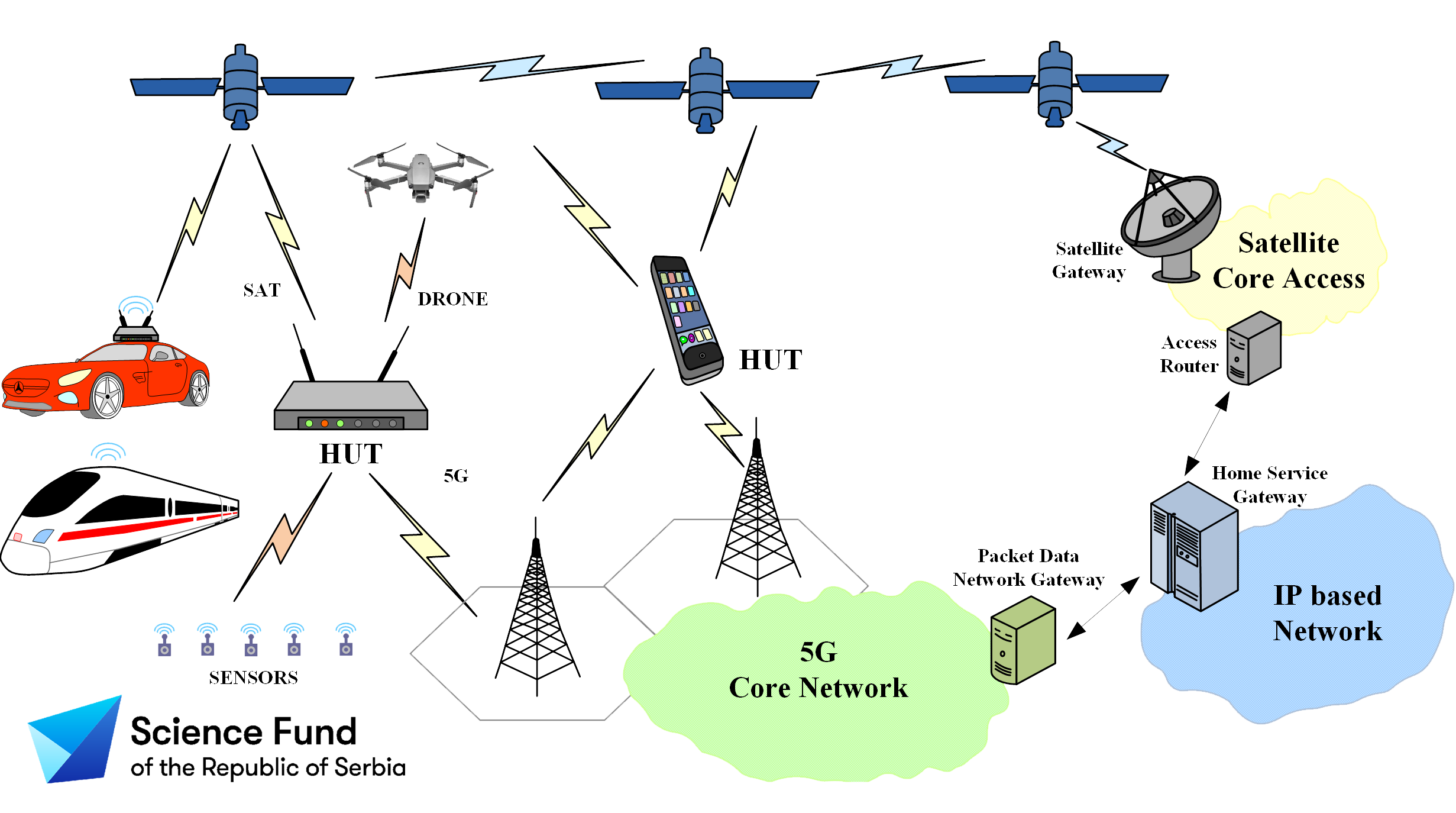

hi-STAR

Funded by: Science Fund

Start date: Jan. 2022

Project lead: dr. Predrag Ivaniš, Telecommunications department

PARTICIPANTSHybrid Integrated Satellite and Terrestrial Access Network (hi-STAR) is a project whose main objective is to develop and implement in hardware a high-performance hybrid access terminal with the ability to steer user traffic between 5G and LEO satellite links, with aid of artificial intelligence methods.

Power efficient, adaptive, multiprocessor and multisensory systems

Funded by: Ministry of Science, Education and Technological Development

Start date: Mar. 2011

Project lead: dr. Ivan Popović, Electronics department

PARTICIPANTS

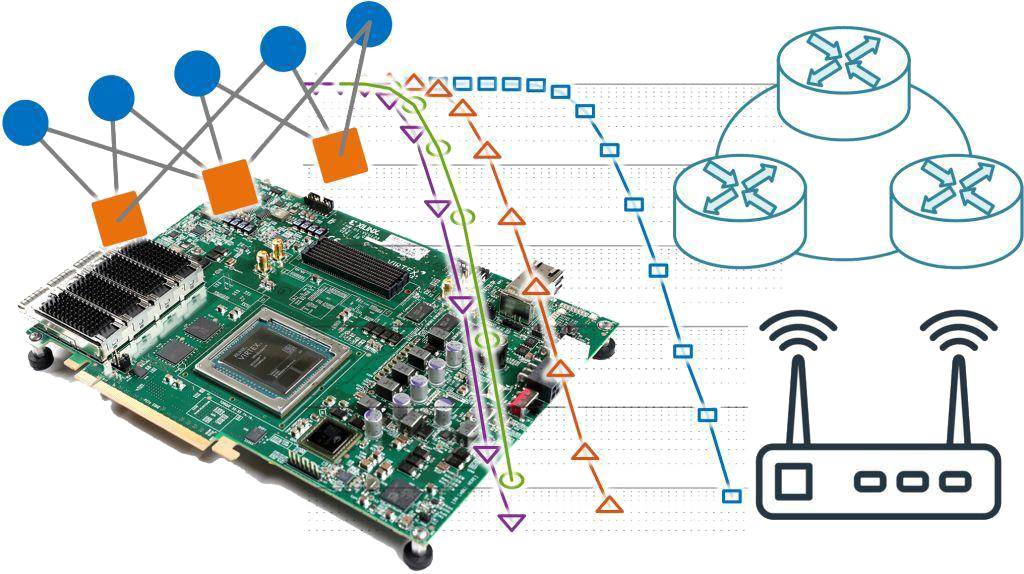

Development of wideband modem and internet switch

Funded by: NTWINE, Tannera

Time span: Apr. 2017 - Dec. 2020

Project lead: dr. Lazar Saranovac, SPARC group

LEAD TEAM

The project is focussed on hardware acceleration of high-end telecommunication systems. The

project is divided to two major parts:

1) Physical layer hardware implementations for satellite DVB-S2(x) and terrestrial 5G NR

standards

The major research was focussed on novel hardware architectures for quasi-cyclic LDPC

decoders and encoders, as well as modulator and demodulator.

2) Development of high-end internet switch

The major research was on development of novel architecture and implementation of a

spaceborne router integrated on an FPGA. The router supported high bit-rate satellite links:

10 Gbps satellite-to-ground links and 100 Gbps intersatellite links.

#Publications: 6

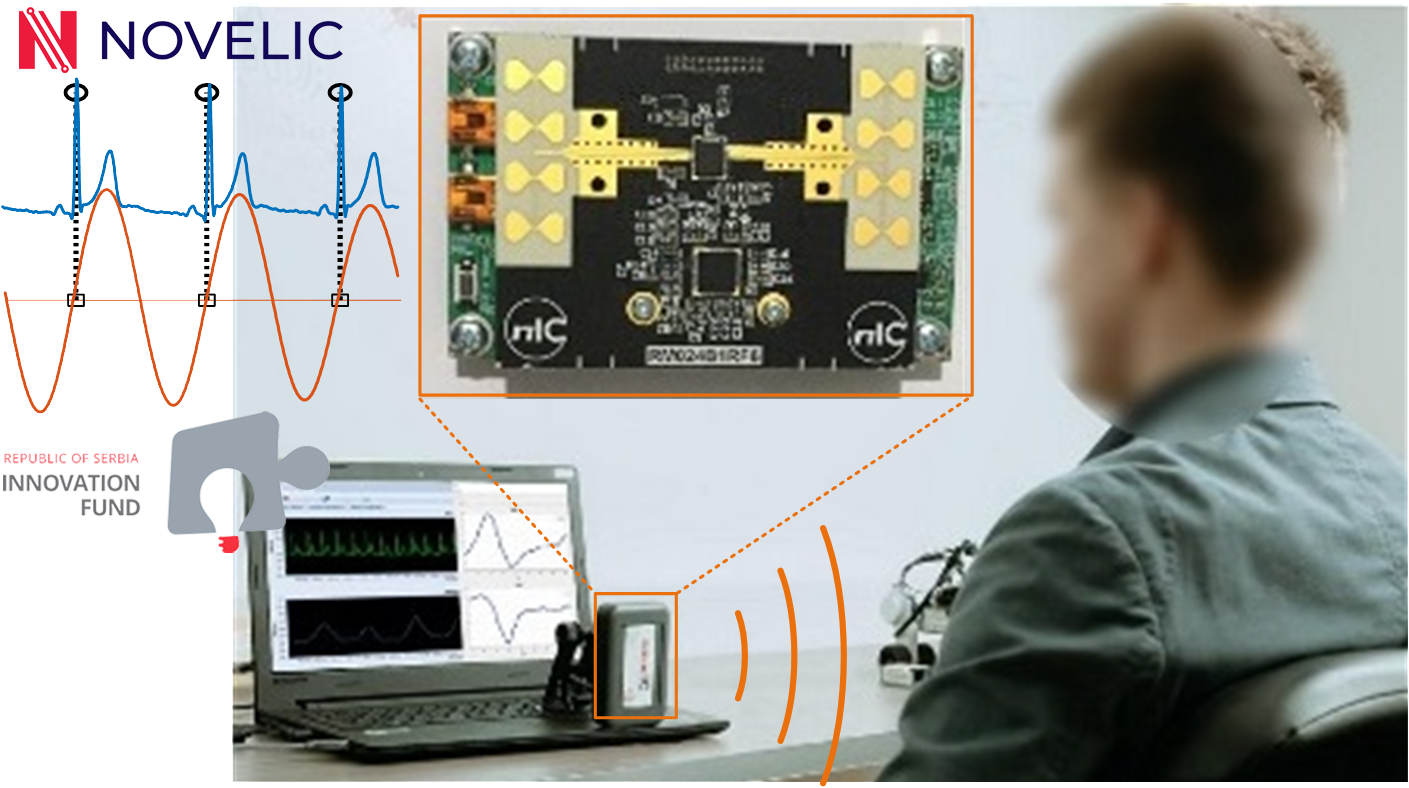

HUDES - Human Detection Sensor

Funded by: Innovation Fund, Novelic

Time span: Feb. 2017 - Feb. 2019

Project lead: dr. Milica Janković, BMIT group

PARTICIPANTS

The project revolves around a novel, unique, low cost and miniature contactless human

detection sensor module, based on radar sensing and advanced detection of human vital

signs and presence. This innovation will find its primary application in the transportation

and auto industry, but can also be applied to various other industries and service sectors,

ranging from entertainment venues such as cinemas and theaters to smart furniture in modern

business environments.

We participated in development of novel algorithms for the estimation of heart rate using

24-GHz continuous-wave Doppler radar with quadrature architecture. The developed algorithms

performed in real-time with high-accuracy estimation of beat-to-beat intervals (BBIs) and

heart rate variability (HRV) features.

#Publications: 3

Computational photography algorithms and architectures

Funded by: Intel corporation

Time span: Sep. 2011 - Sep. 2016

Project lead: dr. Lazar Saranovac, SPARC group

LEAD TEAMDevelopment of the image processing algorithms for enhancing image and video quality of mobile cameras. Main focus was on algorithms for low light imaging and high dynamic range imaging.

#Publications: 4

CONTACT

Address:

University of Belgrade - School of Electrical Engineering

Bulevar kralja Aleksandra 73

Office P-20 or 102v

Belgrade, Serbia

Phones:

+381 11 3218 365

+381 11 3370 167

Email:

sparc[AT]el[DOT]etf[DOT]rs