NEWS

Junior Researcher positions in VLSI signal processing available

Jan. 26, 2022

We are looking for two Junior Research Assistants to work on projects in the field of VLSI signal processing. We are looking for creative, flexible, and self-motivated individuals with excellent communications skills, and a passion for problem solving in a fast-paced team environment.

The official call can be found HERE.

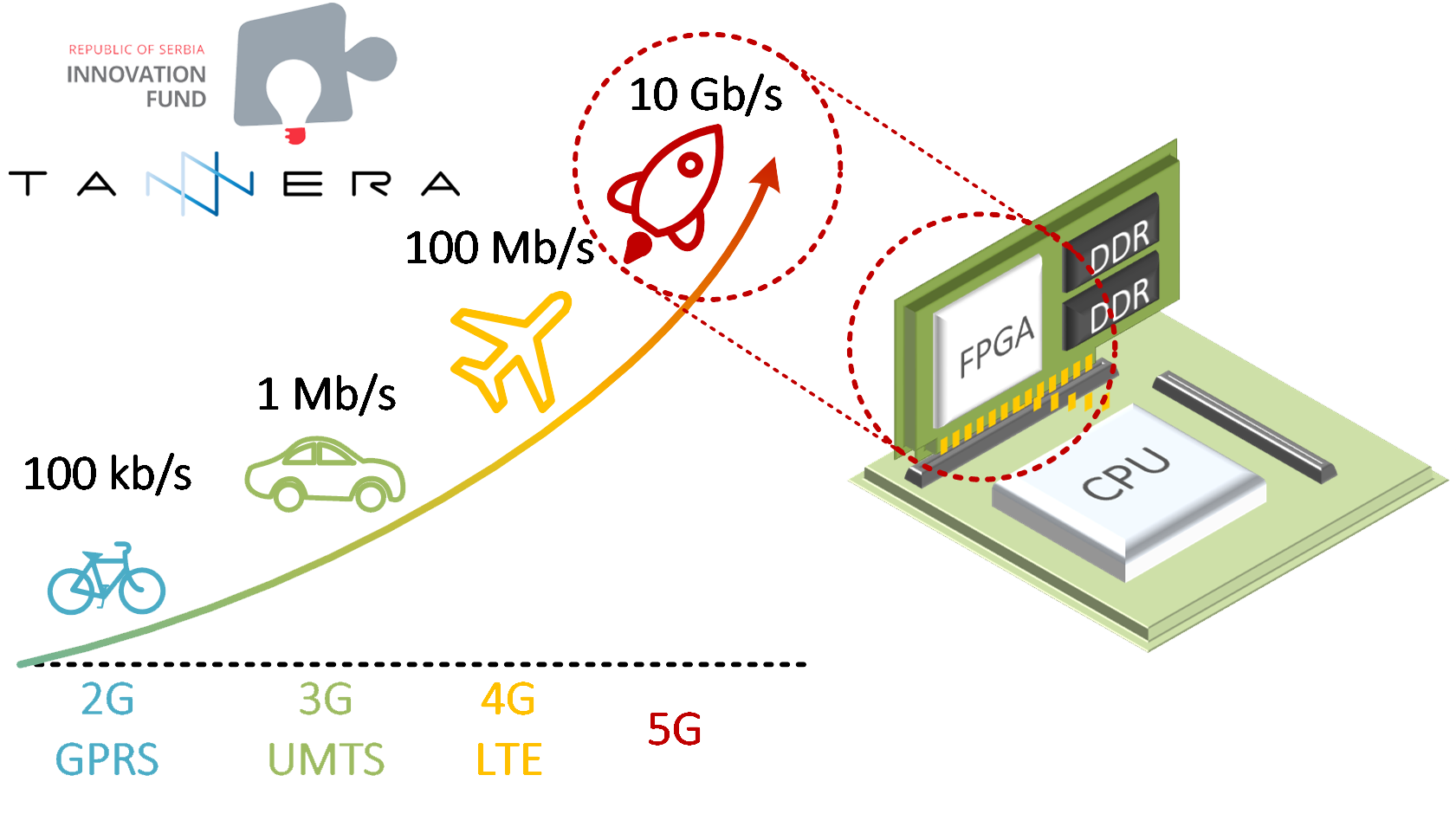

SPARC group received an Innovation Fund Grant

Dec. 31, 2021

Tannera and our research group joined their efforts in developing cutting-edge technology for forthcoming 5G communications infrastructure. We applied and received a grant from the Collaborative Grants Scheme financed by the Innovation Fund of the Republic of Serbia for the project entitled Accelerate 5G: Hardware accelerator IP cores for 5G infrastructure. Accelerate 5G project addresses the design of innovative solutions for physical layer (L1) digital processing acceleration. The solution solves major issues in 5G infrastructure deployment, such as high network deployment costs (CAPEX), high network operation and management costs (OPEX), high throughput and high flexibility demands.

The objective of the project is to develop a full cost-efficient product of an end-to-end FPGA based accelerator for physical layer processing in 5G base stations. The focus is on workloads placed at the distributing units, which include compute intensive tasks, such as forward error correction, modulation, and channel equalization. The product will be in the form of IP cores that can be deployed to any FPGA acceleration card.

Our group will be actively participating in algorithm development and hardware architectures design for channel coding and various signal processing blocks in the physical layer chain.

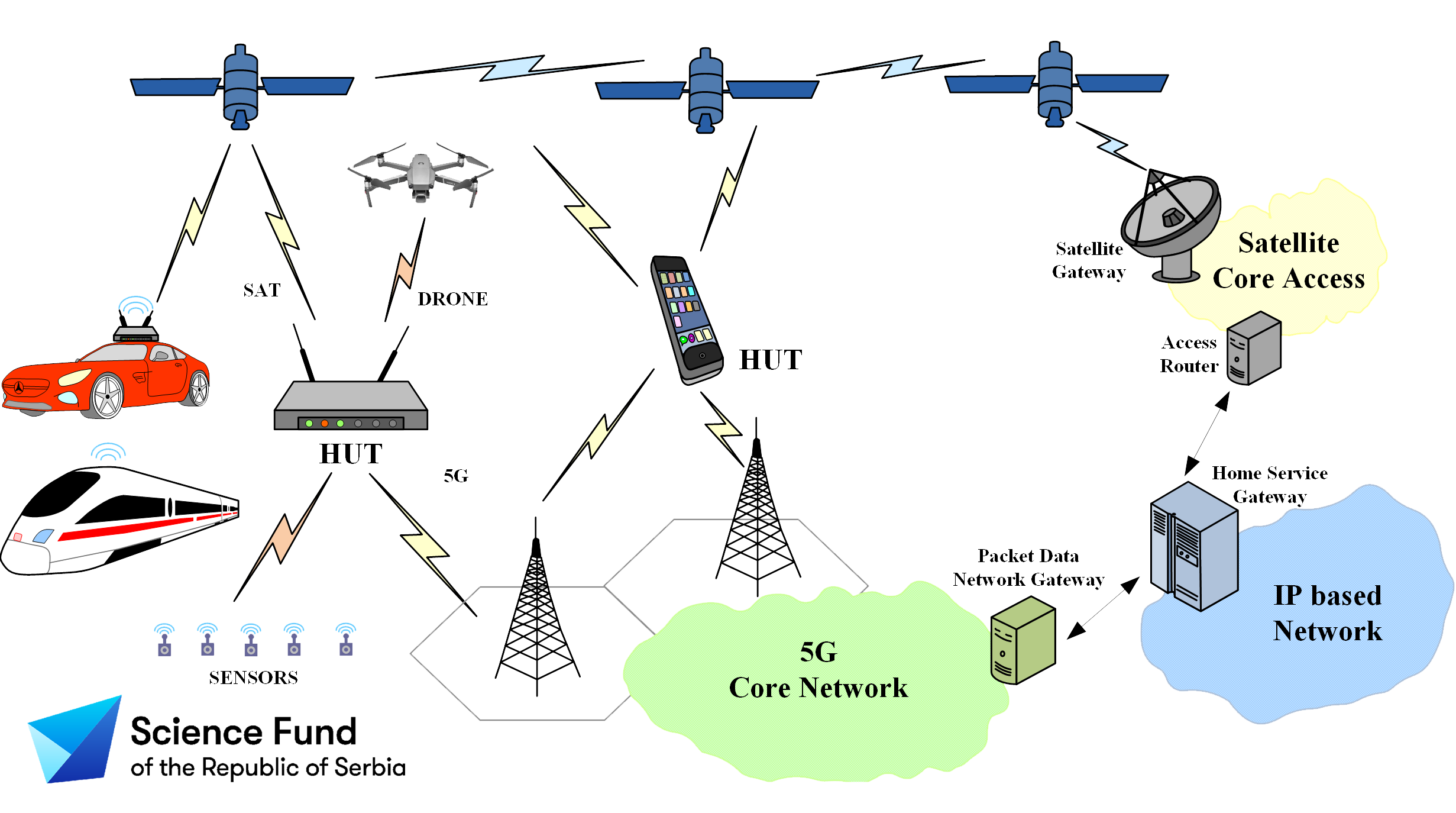

SPARC group participates in a project financed by Science Fund

Dec. 22, 2021

Together with colleagues from the Telecommunications department, we received a grant from the Science

Fund of the Republic of Serbia for developing a hybrid satellite-terrestrial modem.

The main objective of the project is to develop and implement in hardware a high-performance hybrid

access terminal with the ability to steer user traffic between 5G and LEO satellite links, with aid of

artificial intelligence methods.

Our group wil be working on implementation aspects of the hybrid modem (hardware-software co-design,

FPGA design, embedded programming) on an RF-SoC hardware platform. Dr. Lazar Saranovac will be leading

the work package for the hybrid modem implementation, while dr. Dragomir El Mezeni will lead the work

package for the integrated demonstration and proof of concept of the technology.

The project starts on December 29, 2021.

Vladimir Petrović defended his Ph.D. dissertation

Oct. 14, 2021

Our colleague Vladimir Petrović successfully defended his Ph.D. dissertation entitled Flexible Encoder

and Decoder of Low-Density Parity-Check Codes. The defense has been held at the University of Belgrade -

School of Electrical Engineering. Committee members were:

dr. Lazar Saranovac, professor,

University of Belgrade - School of Electrical Engineering

dr. Jelena Popović-Božović, assistant professor,

University of Belgrade - School of Electrical Engineering

dr. Goran Đorđević, professor,

University of Niš - Faculty of Electronic Engineering

dr. Predrag Ivaniš, professor,

University of Belgrade - School of Electrical Engineering

dr. Dragomir El Mezeni, assistant professor,

University of Belgrade - School of Electrical Engineering

dr. Srđan Brkić, assistant professor,

University of Belgrade - School of Electrical Engineering

The dissertation proposes high speed, flexible and hardware efficient solutions for coding and decoding

of highly irregular low-density parity-check (LDPC) codes, required by many modern communication standards.

The first part of the dissertation’s contributions is in the novel partially parallel LDPC encoder

architecture for 5G. The architecture was built around the flexible shifting network that enables

parallel processing of multiple parity check matrix elements for short to medium code lengths, thus

providing almost the same level of parallelism as for long code encoding. In addition, the processing

schedule was optimized for minimal encoding time using the genetic algorithm. The optimization procedure

contributes to achieving high throughput, low latency, and up to date the best hardware usage efficiency

(HUE).

The second part proposes a new algorithmic and architectural solution for structured LDPC code decoding.

A widely used approach in LDPC decoders is a layered decoding schedule, which frequently suffers from

pipeline data hazards that reduce the throughput. The decoder proposed in the dissertation conveniently

incorporates both the layered and the flooding schedules in cases when hazards occur and thus facilitates

LDPC decoding without stall cycles caused by pipeline hazards. Therefore, the proposed architecture

enables insertion of many pipeline stages, which consequently provides a high operating clock frequency.

Additionally, the decoding schedule was optimized for better signal-to-noise ratio (SNR) performance

using genetic algorithm. The obtained results show that the proposed decoder achieves great throughput

increase and the best HUE when compared with the state of the art for the same SNR performance.

The dissertation contributions have been confirmed through several research papers of which two are from

impact factor journals.